# Preliminary CDP1831D, CDP1831CD 512-Word x 8-Bit Static **Read-Only Memory**

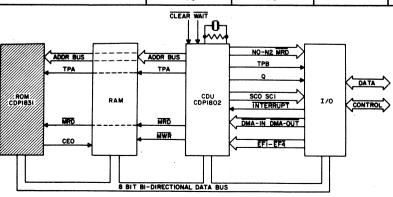

The RCA-CDP1831D and CDP1831CD are static 4096-bit mask-programmable COS/MOS read-only memories organized as 512 words x 8 bits and designed for use in CDP1800series microprocessor systems. They will directly interface with either the CDP1801 or CDP1802 microprocessors without additional components.

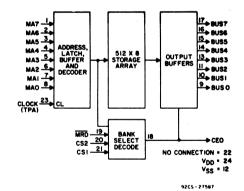

The CDP1831 responds to 16-bit address multiplexed on 8 address lines. Address latches are provided on-chip to store the 8 most significant bits of the 16-bit address. By mask option, this ROM can be programmed to operate in any 512-word byte of 64K memory space. Three Chip-Select signals—CS1, CS2, MRD—are also provided.

MAXIMUM RATINGS,

The polarity of the clock (TPA), and CS1 and CS2 are user mask-programmable. The Chip-Enable output signal (CEO) goes "high"

when the device is selected. This signal is intended for use as an output disable control for small memory systems.

The CDP1831D is functionally identical to the CDP1831CD. The CDP1831D has a recommended operating voltage range of 3 to 12 volts, and the CDP1831CD has a recommended operating voltage range of 4 to 6 volts.

The CDP1831D and CDP1831CD are supplied in 24-lead, hermetic, dual-in-line ceramic packages.

### Features:

- Static Silicon-Gate CMOS circuitry—CD4000-series compatible

- Compatible with CDP1800-series microprocessors at maximum speed

- Interfaces with CDP1801, CDP1802 microprocessors without additional components

- Fast access time: 400 ns typ. at V<sub>DD</sub> = 10 V

- Single voltage supply

- On-chip address latch

- Full military temperature range (-55°C to +125°C)

- Optional programmable location within 64K memory space

- Low quiescent and operating power

#### Absolute-Maximum Values Storage-Temperature Range (T<sub>stg</sub>) -65 to +150°C Operating-Temperature Range (TA) -55 to +125°C DC Supply-Voltage Range (V<sub>DD</sub>) (All voltage values referenced to V<sub>SS</sub> terminal) CDP1831D .....-0.5 to +15 V CDP1831CD ..... -0.5 to +7 V Power Dissipation Per Package (PD): For T<sub>A</sub>=-55 to +100°C

For T<sub>A</sub>=+100 to +125°C ..... Derate Linearly to 200 mW Device Dissipation Per Output Transistor: For  $T_{\Delta} = -55^{\circ}C$  to  $+125^{\circ}C$  ...... 100 mW Input Voltage Range, All Inputs ..... -0.5 to V<sub>DD</sub> +0.5 V Lead Temperature (During Soldering): At distance  $1/16 \pm 1/32$  inch  $(1.59 \pm 0.79 \text{ mm})$

92CM-27585

from case for 10 s max. ......

-CLOCK MA5 -csi CEO MAI - BUS 7 - BUS 6 BUS O BUSI BUSS

NC = NO CONNECTION

Terminal Assignment

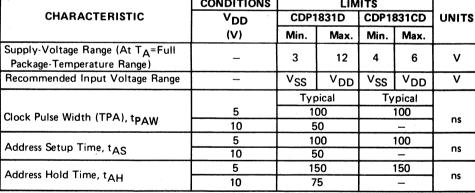

### OPERATING CONDITIONS at TA=25°C Unless Otherwise Specified

For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges:

|                                                                          | CONDITIONS      | LIMITS   |                 |           |                 |       |

|--------------------------------------------------------------------------|-----------------|----------|-----------------|-----------|-----------------|-------|

| CHARACTERISTIC                                                           | V <sub>DD</sub> | CDP1831D |                 | CDP1831CD |                 | UNITS |

|                                                                          | (V)             | Min.     | Max.            | Min.      | Max.            |       |

| Supply-Voltage Range (At T <sub>A</sub> =Full Package-Temperature Range) | _               | 3        | 12              | 4         | 6               | ٧     |

| Recommended Input Voltage Range                                          | <del>-</del>    | VSS      | V <sub>DD</sub> | VSS       | V <sub>DD</sub> | V     |

|                                                                          |                 | Typical  |                 | Typical   |                 |       |

| Clock Pulse Width (TPA), tPAW                                            | 5               | 100      |                 |           | 100             |       |

|                                                                          | 10              | 50       |                 |           |                 | ns    |

| Address Setup Time, tAS                                                  | 5               | 100      |                 | 100       |                 |       |

|                                                                          | 10              | 50       |                 | _         |                 | ns    |

| Address Hold Time, t <sub>AH</sub>                                       | 5               | 150      |                 | 150       |                 |       |

|                                                                          | 10              | 75       |                 |           | _               | ns    |

Fig. 1-Typical CDP1802 microprocessor system.

CDP1832 Functional Diagram

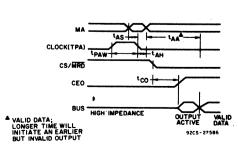

**Timing Diagram**

## Preliminary CDP1831D, CDP1831CD

ELECTRICAL CHARACTERISTICS at TA=25°C

|                                                                    | TEST<br>CONDITIONS |                 | LII      |           |       |  |

|--------------------------------------------------------------------|--------------------|-----------------|----------|-----------|-------|--|

| CHARACTERISTIC                                                     |                    |                 | CDP1831D | CDP1831CD | UNITS |  |

|                                                                    | Vo                 | V <sub>DD</sub> | TYPICAL  | TYPICAL - | }     |  |

|                                                                    | (V)                | (V)             | VALUES   | VALUES    |       |  |

| Static                                                             |                    |                 |          |           |       |  |

| Quiescent Device Current, IL                                       |                    | 5               | 100      | 100       | μΑ    |  |

|                                                                    | _                  | 10              | 500      | _         |       |  |

|                                                                    | _                  | 15              | 1000     | _         |       |  |

| Output Drive Current:                                              |                    |                 |          |           |       |  |

| N-Channel (Sink), I <sub>D</sub> N                                 | 0.4                | 5               | 0.8      | 0.8       |       |  |

|                                                                    | 0.5                | 10              | 1.8      |           | mA    |  |

| P-Channel (Source), IDP                                            | 4.6                | 5               | -0.8     | -0.8      | J ""A |  |

|                                                                    | 9.5                | 10              | -1.8     | _         |       |  |

| Dynamic: t <sub>f</sub> ,t <sub>f</sub> =10 ns, C <sub>L</sub> =50 | pF                 |                 |          |           |       |  |

| Access Time From Address Change, tAA                               |                    | 5               | 850      | 850       | ns    |  |

|                                                                    | _                  | 10              | 400      | -         |       |  |

| Chip Enable Output Delay                                           | _                  | 5               | 400      | 400       | ns    |  |

| Time From CS, t <sub>CO</sub>                                      | _                  | 10              | 200      | _         |       |  |

### Note:

The dynamic characteristics and timing diagrams indicate maximum performance capability of the CDP1831. When used directly with the CDP1802 microprocessor, timing will be determined by the clock frequency and internal delays of the microprocessor.

The following general timing relationships will hold when the CDP1831 is used with the CDP1802 microprocessor:

$$t_{AH} = 0.5 t_{c}$$

$t_{PAW} = 1.0 t_{c}$

MRD occurs one clock period (t<sub>c</sub>) earlier than the address bits MA0-MA7.

where

$$t_c = \frac{1}{\text{CDP1802 clock frequency}}$$

The CDP1831 is capable of operating at the maximum clock frequency of the CDP1802 microprocessor.